#156. 有限状态机

有限状态机

题目描述

下图是摩尔型有限状态机的结构图,我们可以发现其包含三个部分,第一部分为纯组合逻辑,通过现态和输入信号生成次态信号,第二部分为时序逻辑,该时序逻辑非常简单,只包含一个带有复位功能的寄存器单元,复位时现态信号变为初始值,否则在每个时钟的上升沿将次态信号赋值给现态信号。第三部分为组合逻辑,该部分通过现态信号生成各输出信号。

对于上述电路,其Verilog代码实现为:

module traffic_ctrl(

input clk,

input rst,

input timer_pulse,

output green_light

);

parameter C_PASS = 2'b00;

parameter C_TRANS = 2'b01;

parameter C_STOP = 2'b10;

reg [1:0] curr_state;

reg [1:0] next_state;

//有限状态机第一部分

always@(*)

begin

if(timer_pulse)

begin

case(curr_state)

C_PASS: next_state = C_TRANS;

C_TRANS:next_state = C_STOP;

C_STOP: next_state = C_PASS;

default:next_state = C_PASS;

endcase

end

else

next_state = curr_state;

end

//有限状态机第二部分

always@(posedge clk or posedge rst)

begin

if(rst)

curr_state <= C_PASS;

else

curr_state <= next_state;

end

//有限状态机第三部分,各输出信号的赋值都应放在此部分

assign green_light = (curr_state==C_PASS)? 1'b1 : 1'b0;

//...

endmodule

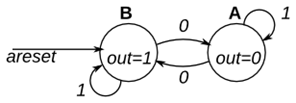

试用Verilog代码实现下图中的摩尔型状态机,有两个状态,一个输入(in),一个输出(out)。实现这个状态机。请注意,电路采用异步复位,复位状态是B。

输入格式

clk areset: Asynchronous reset to state B 1bit in

输出格式

1bit out

示例代码

module top(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);//

parameter A=0, B=1;

reg state, next_state;

always @(*) begin //有限状态机第一段

// State transition logic

end

always @(posedge clk, posedge areset) begin //有限状态机第二段

// State flip-flops with asynchronous reset

end

//有限状态机第三段,信号输出逻辑

// assign out = (state == ...);

endmodule